Huomenna jatkamme Verilogin opiskelua puhtaalla kombinaatiologiikalla ja tätä varten tarvitsemme kehityslaudalle vähintään neljä painiketta ja LEDiä kuten viime torstaina jo osa saikin rakenneltua.

Sitten alamme askel askeleelta opiskelemaan Verilogin kierouksia, olkoon ensimmäisenä wire vs. reg -keywordien käyttö syntetisoituvassa koodissa. Muistisääntö menee lyhyesti näin:

- sijoituksen kohteen pitää olla reg-tyyppiä jos siihen sijoitetaan always-lohkon sisältä, muuten sen pitää olla tyyppiä wire

Se ei siis ole registeri (vaikka mahdollistaa sellaisen luonnin) ja tätä kummajaista on SystemVerilogissa korjattu, mutta sääntö on kuitenkin niin yksinkertainen, että opettelemme sen vain ulkoa kummemmin miettimättä.

Koodit joilla lähdetään liikkeelle löytyvät gitlabista.

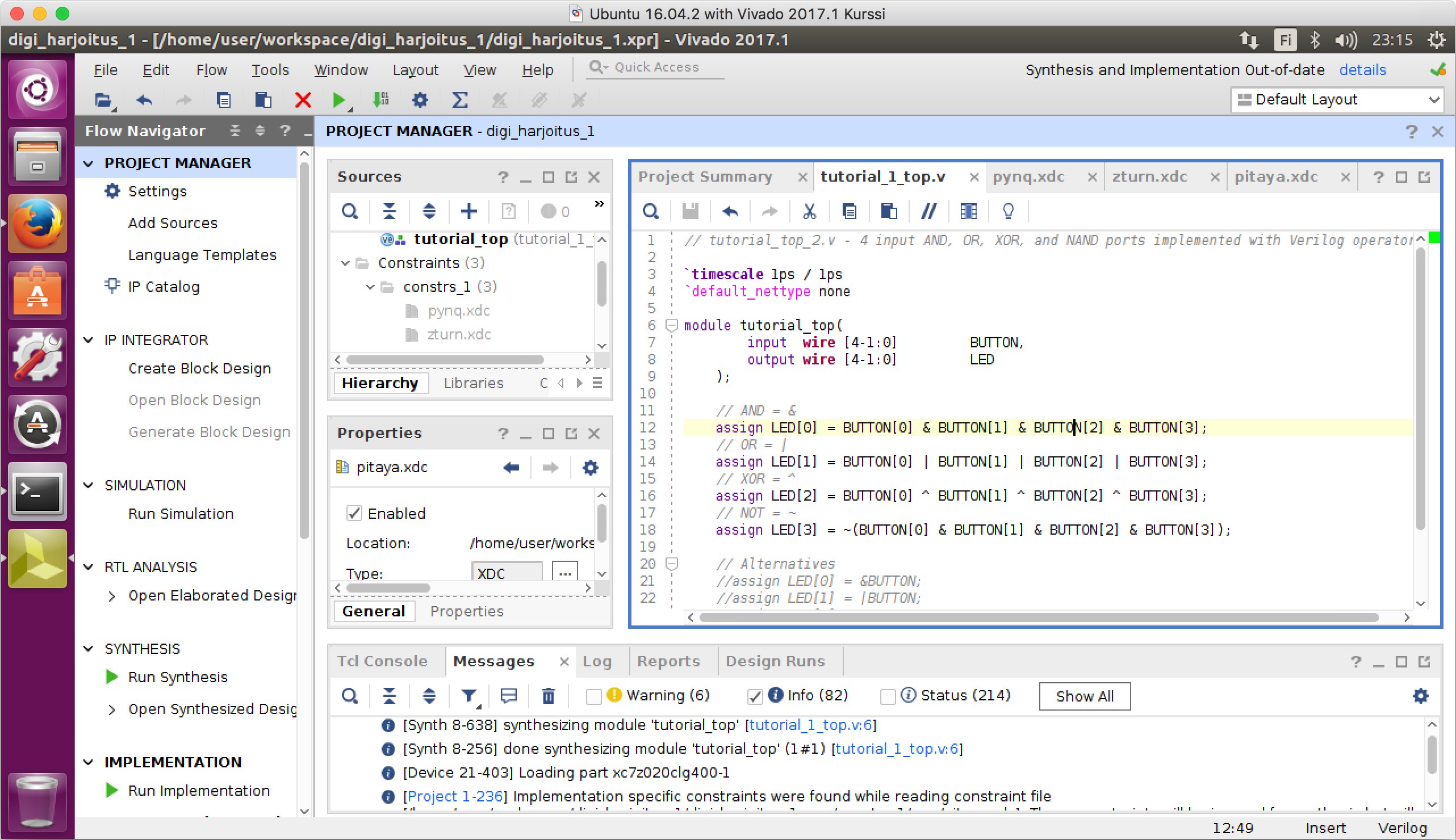

Vivadosta julkaistiin juuri tänään 2017.1-versio ja se näyttäisi toimivan, eli saa päivittää jo tässä vaiheessa jos haluaa, tiedoston Vivado HLx 2017.1: All OS installer Single-File Download (TAR/GZIP - 20.21 GB) - MD5: ee351905f061e19751999e69b41f4b22 voi kopioida labilla muistitikulta. Ulkoasu on vähän uudistunut:

Mainittakoon vielä uutisena, että FPGA-kapasiteettia saa ostaa nyt pilvipalvelunakin, katsastamme tämän sysksyllä paremmin kun siinä on mahdollisuus edullisesti päästä kokeilemaan sen luokan piirejä mihin tuskin yksityisellä henkilöllä olisi muuten varaa.